系统的关键电路模块,存在广泛的应用。本栏将从简单锁相环入手,帮您理解锁相环的基本

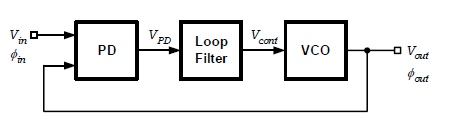

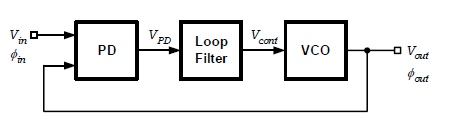

如图为简单锁相环的基本框图包含了三个模块:鉴相器(PD)、环路滤波器(Loop Filter)、压控振荡器(VCO)。只由这三个模块构成的锁相环并没有很好的实用性,但是能很好地帮助读者理解锁相这个概念,对于实际应用中的锁相环,还需要引入电荷泵、分频器等模块,小编将在之后的推送中详细的介绍。本文只针对简单锁相环的分析。

,相位对时间的微分。因此能写出已知频率的正弦波的相位关于时间的表达式:

鉴相器一个熟悉的例子就是异或门(XOR)。当两输入的相位差变化时,输出端的脉冲宽度也相应的变化,从而能够得到一个与相位差成正比的直流电平。

,我们可以通过短时间内提升VCO频率,使VCO更快地积累相位,逐渐减小相位误差。

可知当符合两个条件(1)VCO振荡频率可调(2)有比较两个相位的电路,就可以使VCO输出相位与参考信号相位对齐,对齐的操作被称为“相位锁定”。

但是鉴相器的输出并不是我们希望的直流信号,应此需要在鉴相器和VCO之间引入一个环路滤波器(低通滤波器),抑制鉴相器输出的高频分量。这样就构成了基本的锁相环。

为了后续分析,必须仔细定义相位锁定的条件。书中对相位锁定的定义是:如果VCO相位与参考相位差值不随时间变化,环路就锁定了。将这个定义转换为表达式,就能够获得如下公式。

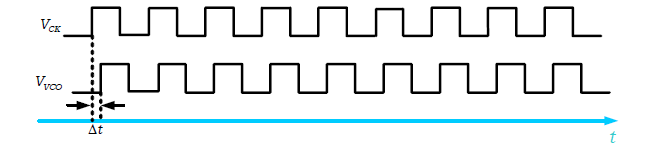

之后我们观察锁定条件下环路各节点的电压波形。在锁定状态下,VCO 输出信号与参考信号频率一致,相位差恒定;而鉴相器输出脉冲宽度恒定;VCO控制电压有较小的脉动,这种脉动被称为“波纹”(ripple),波纹大小受环路滤波器设置影响。

而对于输入输出相位差,我们能够最终靠下式计算。从关系式中我们能够获得两个要点(1)如果锁相环输入频率变化,那么相位误差也同时变化;(2)增大鉴相器和VCO的增益

逐渐升高,VCO输出频率改变,减小相位误差。在这个过程中,VCO频率变化使VCO输出提供增加的相位

观察这个过程我们大家可以归纳两点:1)锁相环回到锁定状态后,所有参数都回到了初始值。2)分析锁相环时,我们很难观察相位和频率随时间的变化,但是振荡器的控制电压确是各很好观测的点。

(Phase Locked Loop),中文名称相位锁栓回路,现在粗略地介绍一下

是一种反馈系统,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。

本帖最后由 zhihuizhou 于 2011-12-21 17:43 编辑

器件选型指导:1) output: Single End clock2) Work Clock: 1Ghz

以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 能够最终靠3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的

)电路设计与应用 /

、整数型频率合成器和分数型频率合成器。下面将详细的介绍这三种模式的作用和特点。 第一种:基本

数明半导体推出一款集成了米勒钳位功能的双通道隔离驱动芯片SiLM8260

项目要做一个DC-DC车载电源,输入300—1000V,输出0—30V,功率大概2KW,前级和后级用什么拓扑比较好?

【RK3568 Android11.0】如何在设置-显示-HDMI-分辨率设置中添加3840*2160的选项?